水平型微指令与垂直型微指令的比较

- 水平型微指令并行操作能力强,指令高效,快速,灵活,垂直型微指令则较差。

- 水平型微指令执行一条指令时间短,垂直型微指令执行时间长。

- 由水平型微指令解释指令的微程序,有微指令字较长而微程序短的特点。垂直型微指令则相反。

- 水平型微指令用户难以掌握,而垂直型微指令与指令比较相似,相对来说,比较容易掌握。

RISC

精简指令计算机。

特点:指令条数少;指令长度固定,指令格式和寻址种类少;只有取数/存数指令访问存储器,其余指令的操作均在寄存器之间进行。

硬布线控制器

PCI总线

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。PCI总线上可以挂接PCI设备和PCI桥片,PCI总线上只允许有一个PCI主设备,其他的均为PCI 从设备,而且读写操作只能在主从设备之间进行,从设备之间的数据交换需要通过主设备中转。

指令周期

CPU从主存中取出二进制代码

从时间来说:取指令事件发生在“取指周期”;数据事件发生在“执行周期”

从空间来说:取出的代码是指令,一定送往指令寄存器(控制器);取出的代码是数据,一定送往数据寄存器(运算器)

原码、补码、反码

> 补码→真值,符号位要算作某个数

原码、补码乘除法

★CRT

例题:CRT分辨率为1024×1024像素,像素的颜色数为256,则刷新存储器的容量是?

$256 = 2^8$,即8位,1字节

$1024×1024×1B=1MB$

CPU寄存器

数据寄存器DR:数据缓冲寄存器,作为CPU和主存、外设之间信息传输的中转站,用以弥补CPU和主存、外设之间操作速度上的差异

指令寄存器IR:保存当前正在执行的一条指令

程序计数器PC:指出下一条指令在主存储器中的地址

地址寄存器AR:保存CPU当前访问的主存单元的地址

累加寄存器AC:通用寄存器

程序状态字寄存器PSW:表征当前运算的状态及程序的工作方式

补码运算

★cache和主存

cache的命中率 $h = \frac{访问cache的次数}{访问cache和主存的总次数}$

主存系统的效率 $e = \frac{访问cache的时间}{平均访问时间}$

设访问cache的时间为$t_c$,访问主存的时间为$t_m$,则$e = \frac{t_c}{h × t_c + (1-h) ×t_m}$

主存和cache同时访问,命中则访问cache,不命中则访问主存

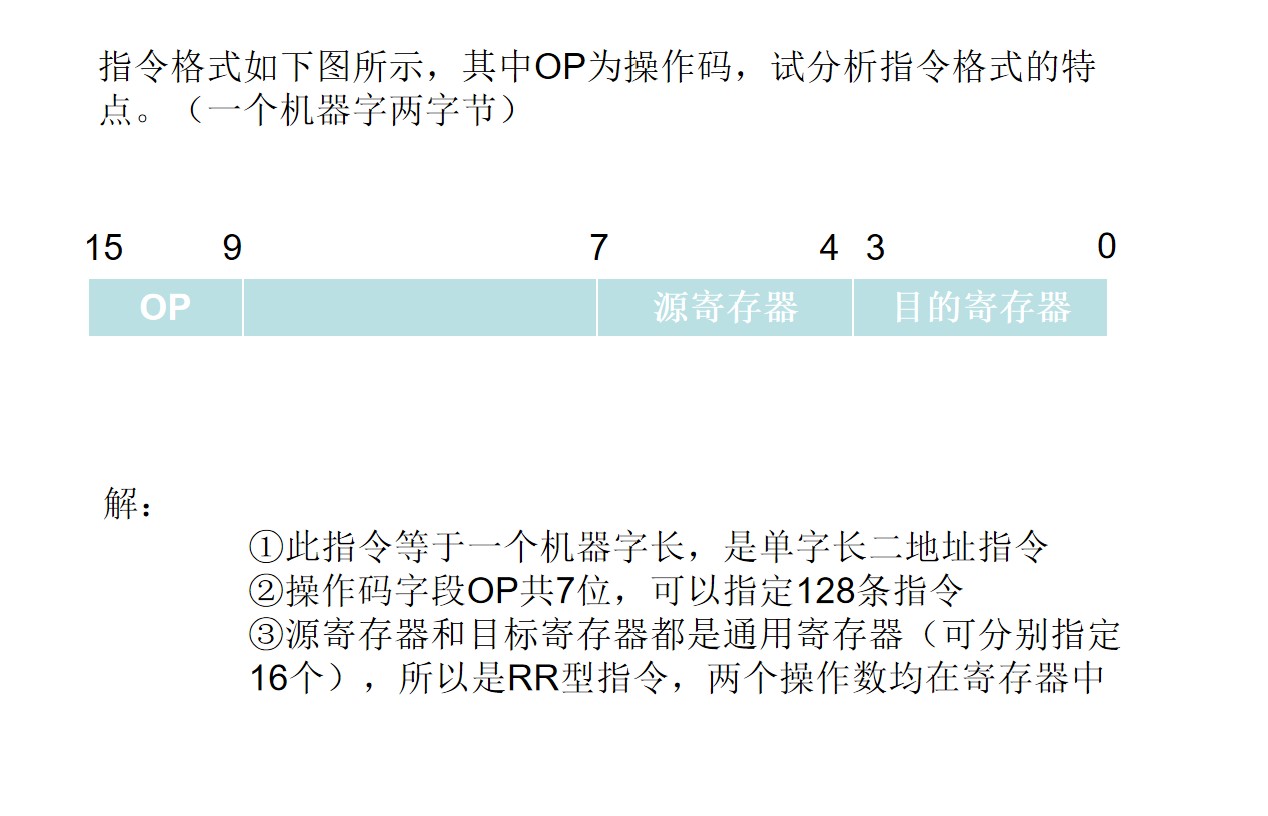

★分析指令格式及寻址方式

例题(背住!!!)

寄存器-寄存器:RR型指令

寄存器-存储器:RS型指令

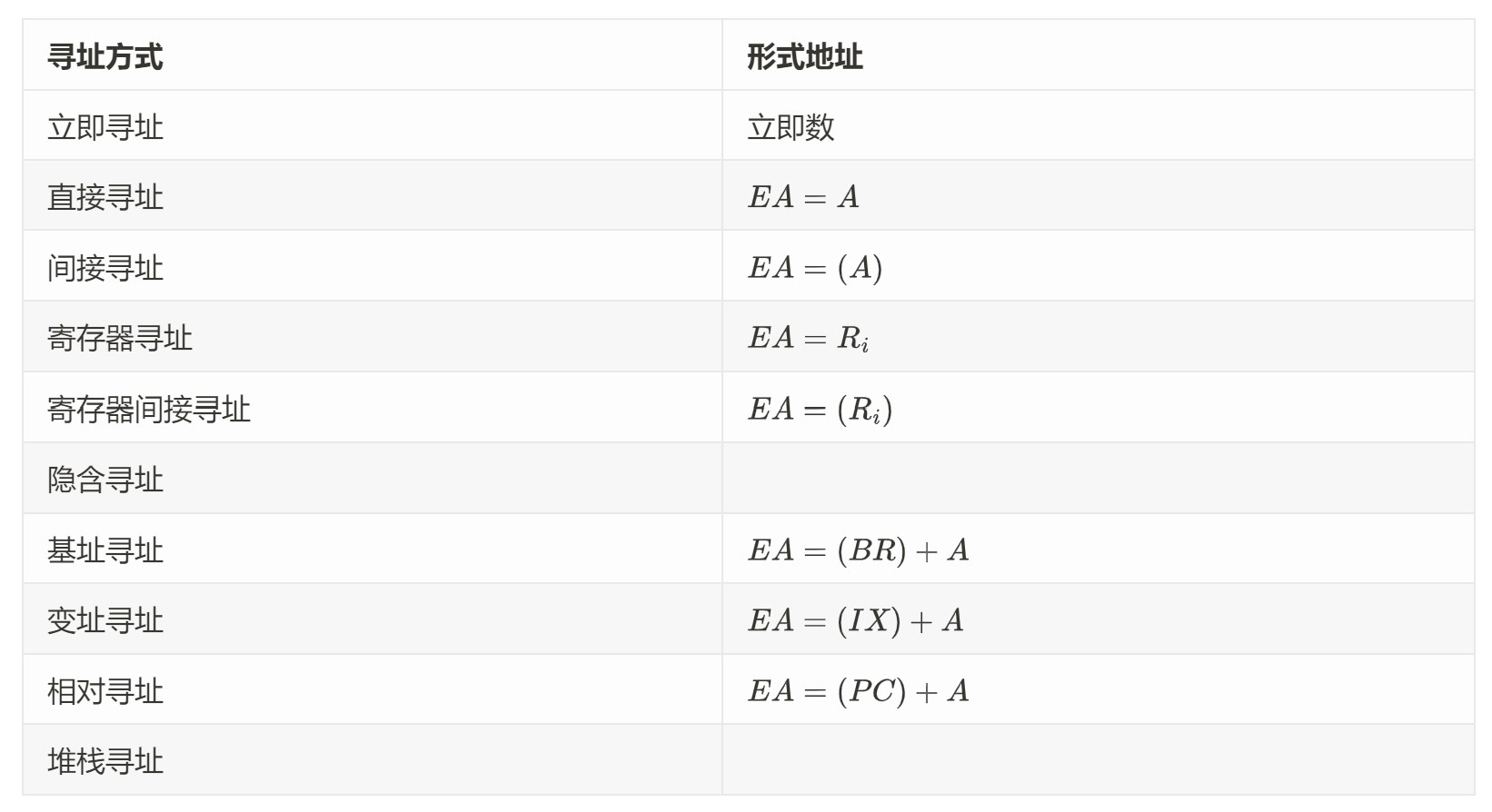

变址寻址一个操作数在寄存器中,一个操作数在存储器中(变址寄存器+位移量A),是RS型指令

★磁盘存储器

$磁盘存取时间 = 平均查找时间 + 平均等待时间$ 平均等待时间记得除以2

$磁盘容量 = 记录面数量 × 磁道数量 × 每道信息量$

$最高位密度(最小半径),最低位密度(最大半径)$

$数据传输率 = 转速(r/s为单位)×每道信息量$

$平均等待时间 = \frac{1}{2}×一秒多少转 =\frac{1}{2}×\frac{1}{转速}$

还是看看作业题吧

★IEEE754

短浮点数:数符位数:1 阶码位数:8 尾数位数:23 偏置值:127

规格化短浮点数的真值为$(-1)^s ×1.M×2^{E-127}$

阶码部分用移码表示,移码E = 真值+偏置值

尾数隐含最高位1

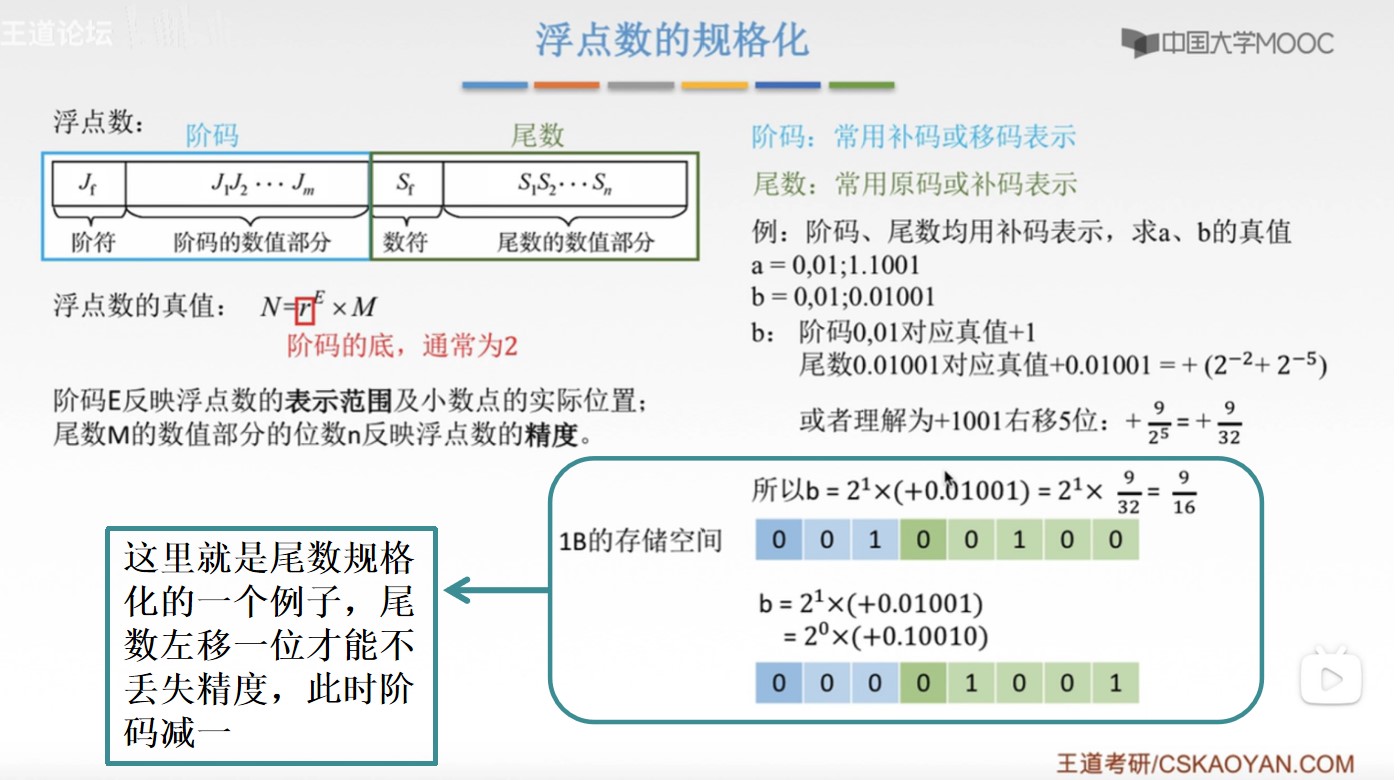

结果规格化

规格化:最高位与符号位相反

先判断结果是不是规格化,如果不是则执行如下操作

- 若结果的符号位为11或00,则进行左规,即尾数左移或小数点右移,阶码在原有基础上减去移动位数

- 若结果的符号位为10或01,则进行右规,即尾数右移或小数点左移,阶码在原有基础上加上移动位数

★CPU地址线、数据线

数据线条数 = 字长位数

地址线n条,则存储单元个数为$2^n$

系统程序区ROM,系统程序工作区RAM,用户程序区RAM

例题,解释得很清楚 注意一些细节问题应该就没事了,细节可以看这个视频,同一道题

考试不允许拍照上传,只能手敲,看起来不用复习画图题了(微笑)

★cache-主存地址映射

★虚拟内存

$页编号长度 = 地址位数-偏移值位数$

有效位:表明此逻辑页是否已存储在主存中

一些可能不重要的概念

> 单地址指令中为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个常需采用隐含寻址方式。

> 广泛使用的SRAM和DRAM都是半导体随机读写存储器,前者的速度比后者快,但存储容量不如后者高。

> 形成指令地址的方式:指令寻址方式、顺序寻址方式、跳跃寻址方式。

> 微型机的标准总线从16位的ISA总线,发展到32位的EISA总线和VESA总线,又进一步发展到64位的PCI总线。

> 为了实现运算器的高速性,采用先行进位、阵列乘除法等并行技术。

> 位操作类指令的功能是对CPU内部通用寄存器或主存某一单元任一位进行状态检测或强置。

> 操作控制器的功能是从主存取出指令,完成指令操作码译码,并产生有关的操作控制信号,以解释执行该指令。

> 3.5英寸软盘记录方式采用双面高密度。

> 通道对CPU的请求形式是中断。

> 一个较完善的指令系统应包含数据传送类指令、算术运算类指令、逻辑运算类指令、程序控制类指令、I/O类指令、字符串类指令、系统控制类指令。

> 并行处理技术已经成为计算机发展的主流。它可贯穿于信息加工的各个步骤和阶段概括起来,主要有三种形式:时间并行、空间并行、时间+空间并行。

> 为了解决多个主设备同时竞争总线,控制权必须具有总线仲裁部件。

> 磁表面存储器的主要技术指标有存储密度、存储容量、平均存取时间和数据传输速率。

> 一个完整的计算机系统应包括硬件和软件。软件又分为系统软件和应用软件两大类。

> 计算机硬件能够直接执行的语言是机器语言。

> 计算机系统中采用补码运算的目的是为了简化计算机设计。

> 在定点加减运算器中,无论采用双符号位还是单符号位,必须有溢出判断,它一般用异或门来实现。

> 在程序执行过程中,cache与主存的地址映射是由硬件自动完成的。

> 程序计数器PC用来存放当前指令的地址,每当执行完一条指令后,通常由程序计数器提供后继指令地址,其位数和主存地址寄存器MAR位数相同。

> 总线主设备指的是可申请并能获得总线使用权的设备。